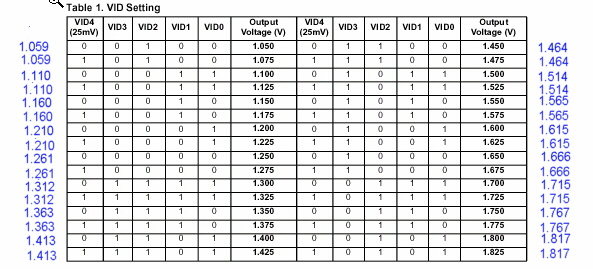

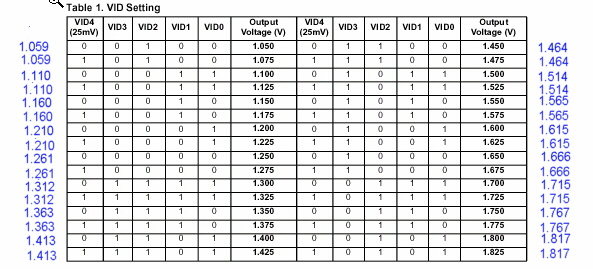

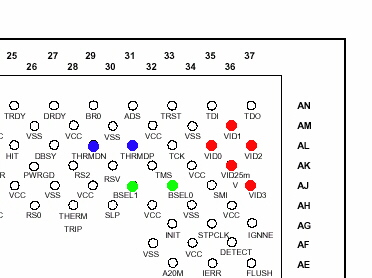

| ↓ PL-iP/3T と Celeron1.2

の電圧情報信号VID線の組み合せ(ST社 L6911Eデータシート抜粋) |

|

青色の文字は、改造後の実測値です。

「0」が、通電:Low

「1」が、絶縁:High

|

『1.875VでFSB133が安定』というのは、間違いですね。

IntelのTualatinコア/PL-iP3/Tに1.875Vの設定はありません。

1.850Vのピンアサインは「00100」 ->

1.050V

1.875Vのピンアサインは「10100」 ->

1.075V

1.900Vのピンアサインは「00011」 -.>

1.100V

1.100V程度でFSB133が安定したら、お化けです。

2の5乗=>32通りしかないことを、ご理解ください。 |

| |

|

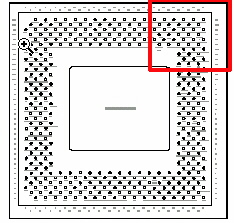

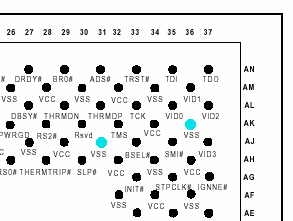

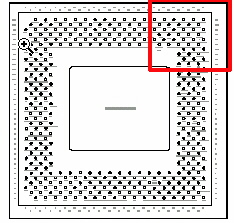

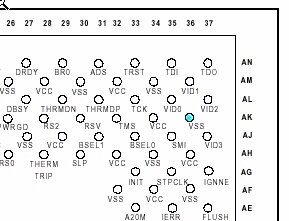

| ↓ 今回の改造対象となる信号線は、Celeron1.2の裏側右上に集中しています。 |

| ピン配置図の全体像 |

Celeron1.2(Tualatinコア)のピンの名称・機能 |

|

|

| |

VID系=電圧情報

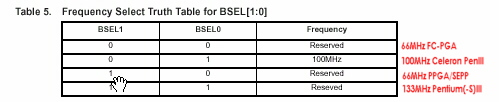

Bsel系=ベースFSB情報

THRM系=サーマルダイオード情報 |

| |

|

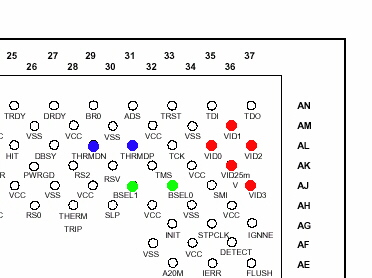

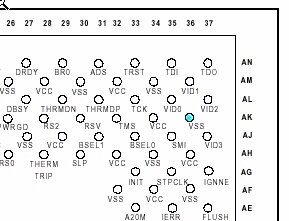

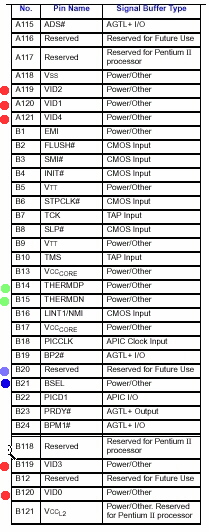

| ↓ 旧コアのCeleronのピンアサイン情報 |

|

|

FC-PGA(Coppermine)の情報

VID4信号がありません。

→Bsel信号とあわせて、Coppermineコア

と認識させるようです。電圧は1.425V

からの生成となります。 |

PPGA(Mendocino)の情報

VID4信号と、BSEL1信号がありません。

→Mendocinoコアと認識させるようです。

電圧は1.800Vからの生成となります。

|

| |

|

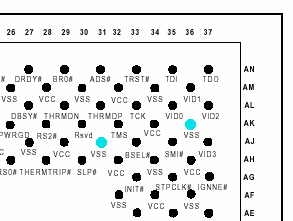

| ↓ Celeron(Mendocino)コアのSEPPパッケージの端子番号とピンアサイン |

|

下駄の改造をする上で、非常に参考になります。

赤●が、VID信号系の端子

SECCパッケージのオーバークロック時に、

端子マスクで、大変お世話になりましたね。

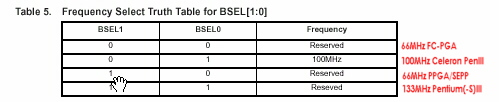

青●が、BSELピン、ベースFSBタイプ信号の端子。

これも、SECCパッケージ時代の秘儀でしたね。

B20は「Reserved」でしたから、

『B21』マスク -> PentiumFSB100騙し!として、

オーバークロックには必須のマスクでした。

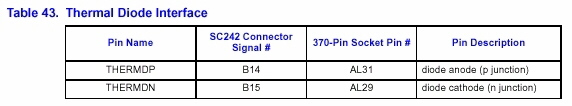

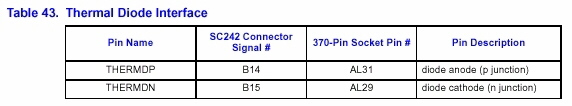

緑●が、サーマルダイオード情報を伝えるTHERM系の端子

B14がPPGA/FC-PGAのAL31ピンに相当

B15が 〃 AL29ピンに相当

下駄の端子がソケットのピンに配線されていないと、

温度を監視することができません。

初期の下駄では、配線を省いてありました。

ソケットのピンの位置と、下駄の端子の位置が正反対に、

遠く離れており、配線パターンが複雑になるためと思わ

れます。どこかで、スルーホールで、内装基盤に落として

やり、2層目か3層目を迂回させてやる必要があります。

この当りは、私のMS-6905Dの記事をご覧下さい。

残念ながら、PL-iP3/Tでは、全く結線されていません。

手抜きはあかんぜよ~!

|

| ↓ サーマル・ダイオード線のピンアサインです。 |

|

| ↓ BSEL信号線のピンアサインです。今回は、改造の対象としませんでしたが・・・。 |

|

| |

|

| 次に、PL-iP3/Tに載っているDC-DCコンバーターの「ST社 L6911E」の分析です。(データシート抜粋) |

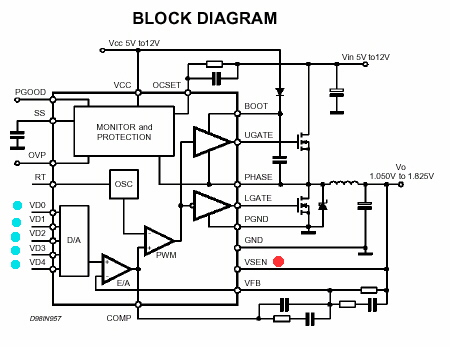

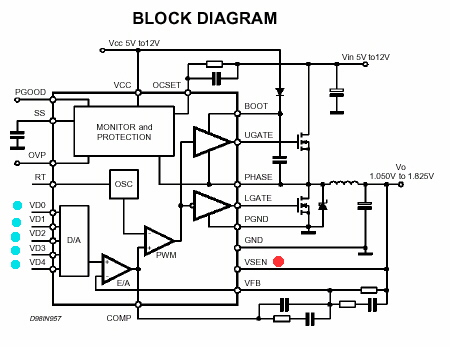

| ↓ L6911E の電気系統図 |

|

今回、改造の対象となる電気系統図です。

青●が、CPUから来るVID0~4信号の入力端子。

赤●が、生成後の電圧+を測るための「VSEN」端子。

本来は過電圧検出用の、生成電圧の戻し端子です。

なお、マイナス(GRAND)は11番端子でも取れますが、

今回は信号の安定度を図る意味でも、電源のGND

(電源3ピンコネクターの真中のピン)に繋ぐことに

しました。 |

| |

|

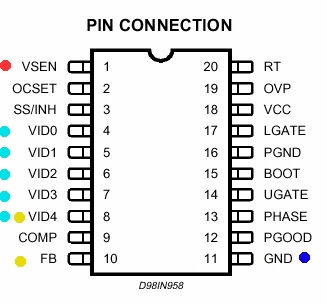

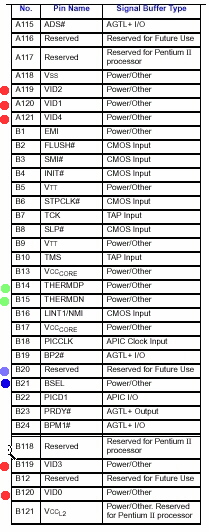

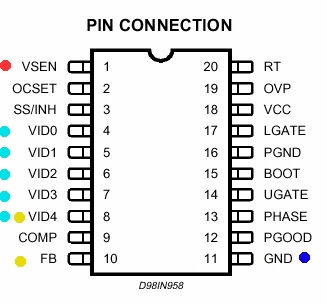

| ↓ L6911E のピンアサイン |

|

青●が、CPUから来るVID0~4信号の入力足。

赤●が、生成後の電圧+を測るための「VSEN」足。

本来は過電圧検出用の、生成電圧の戻し足です。

青●は今回使いませんがマイナス(GND)足。

黄●が、今回発見した、驚くべき事実。

PL-iP3/Tを改造された先達HIROMIさんによると、

『生成電圧が0.05V刻みになる』とのこと。

私も改造後、同じ結果になり、導通を調べてみました。

VID4足は10番のFBに導通し、GNDに落ちています。

絶えずGNDに「通電:Low:0」になっています。

HIROMIさんの改造、疑問は正しかったのです。

上のVID組みあわせ表で、VID4の「1」の16通りは、

ないことになるのです!

どこで、VID4をFBに繋ぎGNDに落としているかは、

L6911Eを剥がせばわかると思います(^^ゞ

なぜ、Powerleap社が、このようにしたかですが、

Coppermineコアとの互換性のためだと思われます。

|