パターンカット部分の復旧+スイッチ改造

| PL-iP3/T Perfect Remodeling [5] |

BXマザーの救世主『PL-iP/3T』の完全改造法(2)です。

結線法とVID信号の挙動を検証するための追加改造の紹介です。

2002.02.17 Takapen Signed 2002.02.18 Updata

PL-iP3/T Perfect

Remodeling(5) 結線法検証改造編

結線法の全パターンの検証をしようと、手抜きで銅線を全ピンから引き出して実験していたのですが、

ショートさせてPL-iP3/Tを2枚潰してしまいました。

安全に実験するためと、CPUからくるVID信号と結線法が合成された場合の挙動を調べるため、

追加の改造を施しました。

| VID信号+結線法の合成挙動問題と、「1」認識の閾値仮説 パターンカットを行わず、VID信号と結線法が合成された場合の挙動については、 いろいろな結果報告がされており、未だ定かではありません。 PL-iP3/Tの個体差か?、Tualatinの個体差か?VID0、VID1の信号を読み間違えることがあるようです。 TualatinのVID信号「1」は、完全に絶縁されておらず、微弱ですが電位がかかっています。 これを相当の抵抗をいれてGNDラインに落とすことで、「1」Highの状態に見せかけているようです。 チップL6911Eが、どのくらいの電圧で「0」Lowと認識するか、「1」Highと認識するかは、 チップL6911Eが固有の閾値を持っているはずです。 TualatinからのVID信号「1」Highの信号は、L6911Eの通電/絶縁判定の閾値前後にあるため、 「1」と読んだり「0」と読んだりする困った現象が起きているのだと思っています。 Ultra66->FT66改造時に、何Ωの抵抗を挟むか?でいろいろな試行錯誤がありました。 チップの反応電圧に閾値があったことを、ご記憶の方もあると思います。同様の理屈・現象です。 この「1」High状態の仕様が、Coppermineコアから変更されているようで、 PL-iP3/Tはこれに完全に対応できていないようです。 Tualatin側の仕様変更と思われますが、対応しきれていないという点では、 PL-iP3/Tは未完成の状態といえるかもしれません。 唯一の問題回避策は、PL-iP3/Tの自動認識を捨て、パターンカットで手動設定に変えることです。 |

パターンカット部分の復旧+スイッチ改造

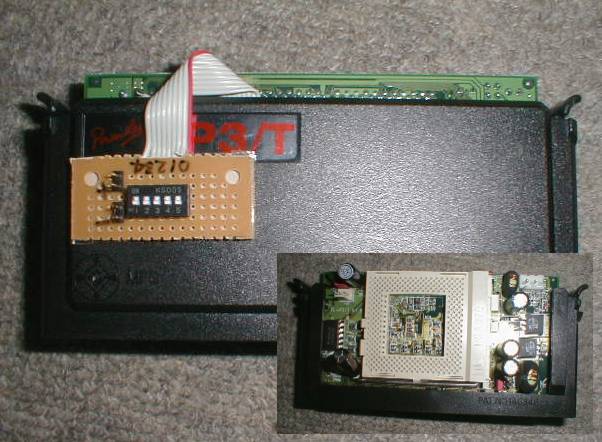

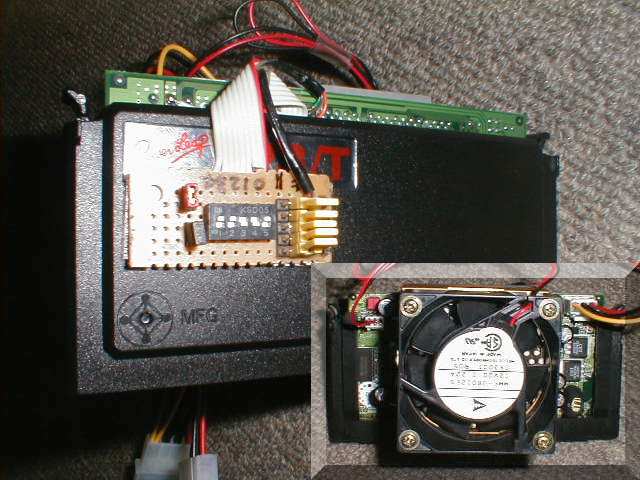

| ↓ Perfect Remodeling(2)の段階の完成写真。Vcore可変、コア温度検出機能付き | |

|

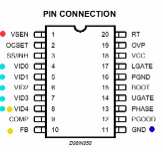

L6911Eのピンアサイン |

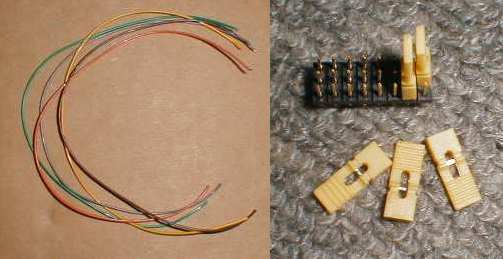

| ↓ 今回の改造の材料です。 | |

|

リード線 (SCSIケーブルから取り出した) 3連ジャンパーポスト ジャンパーピン |

| ↓ リード線をソケット裏のピンの足にはんだ付け | |

|

作業が終わったら、 断線防止の意味でも、 熱収縮チューブで 束ねておくとよいでしょう。 |

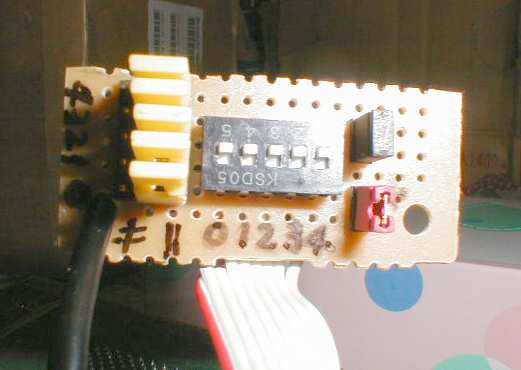

| ↓ ジャンパーを基盤にハンダ付け | |

|

今回の改造は当初から 行うかもしれないと思っ ていたので、基盤にポス トを立てるスペースを確 保していました。 基盤の空いているところ |

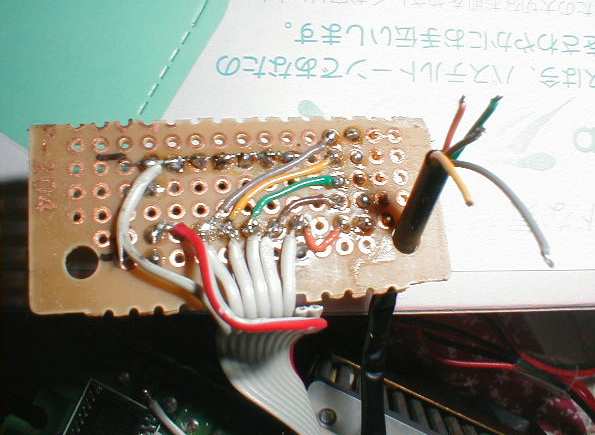

| ↓ ジャンパーとL6911EのVID足から引き出した線のハンダ付け | |

|

リード線の一方を、 基盤のディップスイッチ の足の部分でハンダ。 もう一方を、 |

| ↓ CPUソケットからのリード線をジャンパーポストの足にハンダ | |

|

|

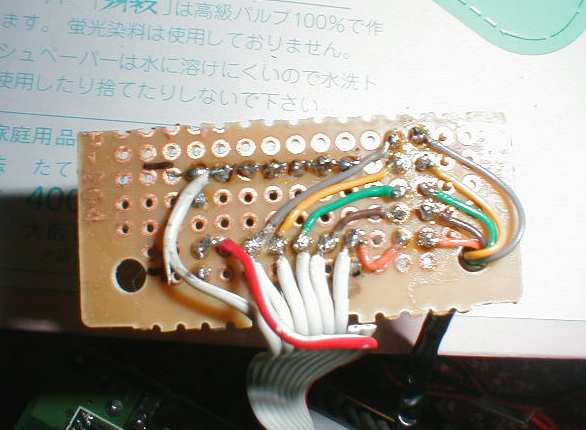

| ↓ 完成した雄姿?です。 | |

|